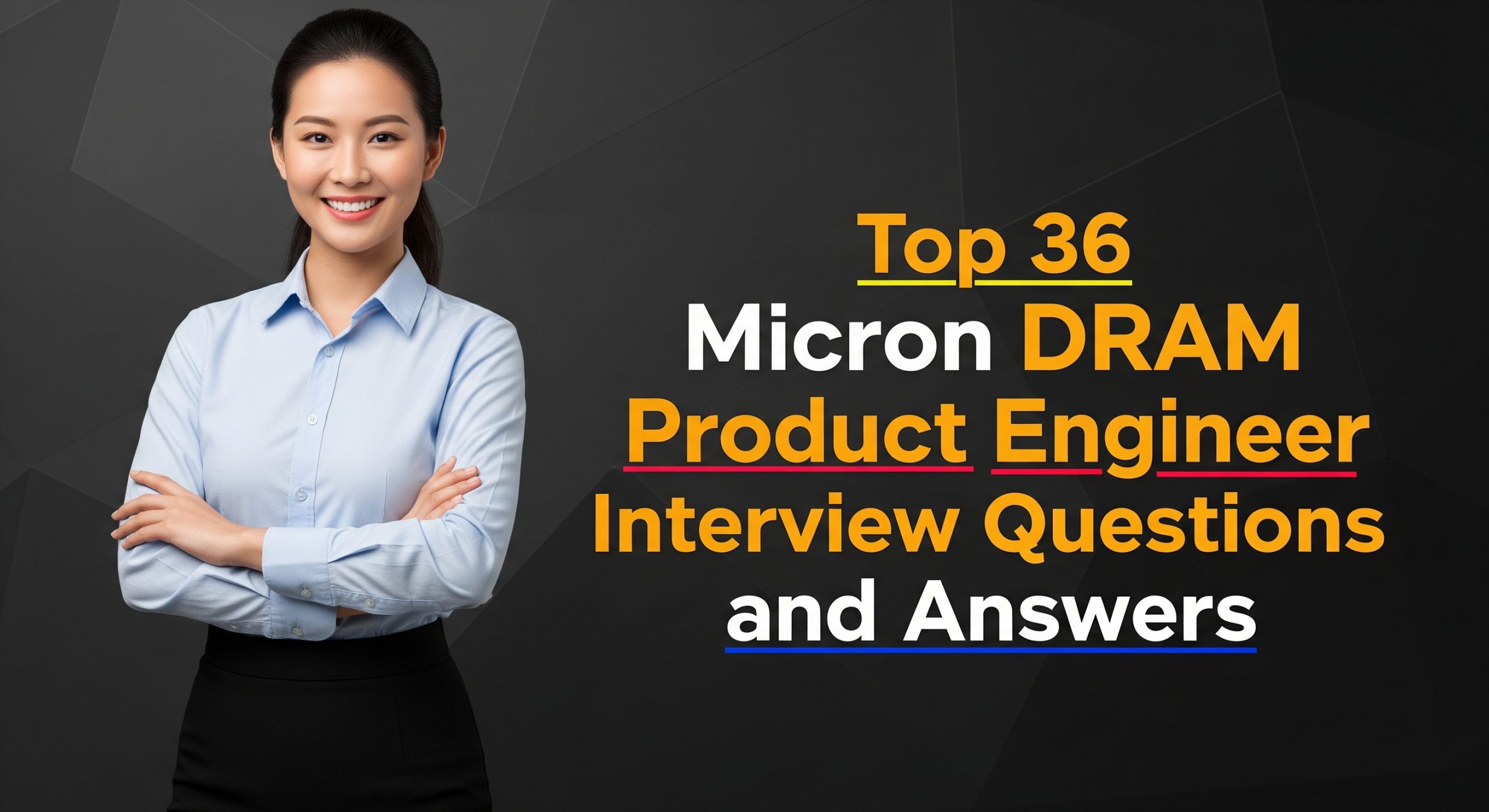

Micron Technology, one of the leading companies in memory and storage solutions, has been at the forefront of innovation in DRAM (Dynamic Random Access Memory) technology. As the demand for high-performance memory in a range of applications—from consumer electronics to enterprise data centers—continues to grow, Micron’s DRAM product engineers play a crucial role in designing, testing, and optimizing these essential components.

If you’re preparing for an interview for the position of a DRAM Product Engineer at Micron, it’s important to have a clear understanding of both technical and behavioral aspects of the job. In this guide, we’ll walk through the top 36 Micron DRAM Product Engineer interview questions to help you prepare effectively. Each question includes an in-depth explanation to ensure you’re fully equipped to tackle even the most challenging aspects of the interview.

Top 36 Micron DRAM Product Engineer Interview Questions

1. What are the main responsibilities of a DRAM product engineer at Micron?

As a DRAM product engineer at Micron, your responsibilities include designing, testing, and optimizing DRAM memory products. You will work closely with cross-functional teams to ensure the product meets performance, quality, and cost targets while staying aligned with customer requirements.

Explanation

Understanding your role and its responsibilities helps interviewers assess whether you can meet the demands of the job and contribute to the company’s success.

2. Can you explain the working principle of DRAM technology?

DRAM (Dynamic Random Access Memory) works by storing each bit of data in a memory cell consisting of a capacitor and a transistor. The capacitor holds a charge to represent a binary ‘1’ and discharges to represent a ‘0’. The data must be refreshed periodically due to the leakage of charge.

Explanation

This question tests your understanding of DRAM at a fundamental level, which is critical for a product engineer working in this field.

3. How do you approach optimizing DRAM for power consumption?

Optimizing DRAM for power consumption involves reducing voltage levels, managing clock speeds, and improving refresh rates. Techniques such as low-power idle modes and burst accesses can also contribute to minimizing power consumption without compromising performance.

Explanation

In DRAM design, power efficiency is a key factor, especially for mobile and embedded applications, where battery life is critical.

4. Describe the process you follow for testing a new DRAM product.

Testing a new DRAM product includes several phases: functional testing, stress testing, and performance benchmarking. Simulations are performed to predict how the DRAM will behave under various conditions, followed by validation on hardware platforms.

Explanation

Effective testing ensures the reliability and stability of DRAM products, which is a crucial part of a product engineer’s role.

Build your resume in just 5 minutes with AI.

5. What challenges have you faced in designing or optimizing DRAM products?

Challenges in DRAM design often include trade-offs between speed, power consumption, and manufacturing cost. Another issue could be dealing with process variations during fabrication, which can impact the performance and yield of DRAM chips.

Explanation

This question helps interviewers understand your problem-solving skills and your ability to handle industry-specific challenges.

6. How do you ensure quality and reliability in DRAM products?

Ensuring quality and reliability involves thorough testing, including thermal cycling, voltage stress tests, and endurance tests. Collaboration with the manufacturing team is essential to identify and mitigate failure points early in the process.

Explanation

Quality and reliability are paramount in DRAM design, as even minor defects can lead to significant failures in end-user applications.

7. Can you explain what DRAM refresh is and why it is necessary?

DRAM refresh is the process of periodically recharging the capacitors in the memory cells to prevent data loss due to charge leakage. Without refreshing, the data stored in the DRAM would eventually disappear.

Explanation

This question tests your knowledge of the core function of DRAM memory and its limitations, a crucial aspect of product engineering.

8. How do you handle design trade-offs between speed and power in DRAM?

Handling trade-offs between speed and power involves selecting the right clock frequencies, voltages, and data rates based on the application requirements. Sometimes sacrificing speed can lead to significant power savings, which is critical for battery-operated devices.

Explanation

Balancing speed and power is one of the key design challenges in DRAM engineering, and understanding how to navigate these trade-offs is essential.

9. Describe a time when you had to troubleshoot a DRAM failure.

During testing, a DRAM chip exhibited intermittent failures under high temperature conditions. By using diagnostic tools and stress testing, I traced the issue to a timing violation in the design, which was corrected through clock adjustments.

Explanation

Interviewers ask this to assess your troubleshooting skills and how you handle failure analysis in complex DRAM systems.

10. How do you stay updated on the latest trends in memory technology?

I stay updated by attending industry conferences, reading research papers, and participating in online forums and webinars focused on semiconductor and memory technology. Additionally, I collaborate with peers and colleagues in the industry.

Explanation

Staying informed about advancements in memory technology is crucial in a rapidly evolving field like DRAM engineering.

11. What is your experience with semiconductor fabrication processes?

I have experience working with various semiconductor fabrication processes, including photolithography, etching, and doping. Understanding these processes is essential for designing DRAM products that can be reliably manufactured at scale.

Explanation

Knowledge of semiconductor processes is fundamental to the design and production of DRAM, which relies on advanced manufacturing techniques.

12. How do you verify the functionality of a DRAM design before fabrication?

Before fabrication, I verify the functionality of a DRAM design using simulation tools that replicate the behavior of the memory cells under different operating conditions. This process helps identify potential issues early.

Explanation

Simulation and verification are crucial steps in ensuring that a DRAM design meets the required specifications and performance standards.

13. Can you explain the significance of memory bandwidth in DRAM?

Memory bandwidth refers to the amount of data that can be transferred between the DRAM and the CPU per second. Higher memory bandwidth is crucial for performance-intensive applications, such as gaming and data processing.

Explanation

Understanding memory bandwidth is essential for optimizing DRAM products to meet the demands of various applications.

14. What steps do you take to improve the yield of DRAM products?

Improving yield involves optimizing the design for manufacturability, reducing process variation, and working closely with the fabrication team to fine-tune the production process. Regular monitoring of key parameters is also crucial.

Explanation

Yield improvement is a critical aspect of DRAM production, as higher yields directly impact cost efficiency and product availability.

15. How do you approach debugging a DRAM-related issue in a system?

Debugging involves using logic analyzers, oscilloscopes, and memory testers to capture data at different stages of operation. I work systematically, isolating potential causes and applying fixes based on the observed behavior.

Explanation

Debugging is an important skill for product engineers, as it ensures that DRAM products function correctly in real-world applications.

16. How do you design DRAM to meet the thermal constraints of modern systems?

Designing DRAM for thermal constraints involves optimizing power consumption, implementing dynamic power management techniques, and selecting materials that dissipate heat efficiently. Ensuring the memory operates within safe thermal limits is essential for long-term reliability.

Explanation

Thermal management is a critical consideration in DRAM design, particularly in high-performance systems where overheating can cause failure.

Planning to Write a Resume?

Check our job winning resume samples

17. What tools do you use for DRAM circuit design and simulation?

I use tools like SPICE for circuit simulation, Cadence for layout design, and Synopsys for verification. These tools allow me to model the behavior of DRAM circuits under different conditions and optimize their performance.

Explanation

Using the right tools is essential for efficient and accurate DRAM design, allowing engineers to simulate and test their designs before fabrication.

18. Can you explain the role of error correction in DRAM?

Error correction in DRAM involves using techniques like ECC (Error-Correcting Code) to detect and correct bit errors. This is crucial in applications where data integrity is paramount, such as in servers and mission-critical systems.

Explanation

Error correction enhances the reliability of DRAM, which is especially important in environments where data corruption can have serious consequences.

19. How do you handle challenges related to DRAM scaling?

As DRAM scales down to smaller process nodes, challenges like increased leakage current, reduced cell capacitance, and higher susceptibility to noise arise. Addressing these requires innovations in materials, circuit design, and process technology.

Explanation

Scaling is a major challenge in the semiconductor industry, and handling it effectively is critical for future DRAM development.

20. Can you describe the differences between DRAM and SRAM?

The main difference between DRAM and SRAM is that DRAM uses capacitors to store data and requires periodic refreshing, while SRAM uses flip-flops and does not require refreshing. SRAM is faster but more expensive and consumes more power than DRAM.

Explanation

Understanding the differences between memory types is important for a DRAM product engineer, as it influences design decisions based on application requirements.

21. How do you approach design validation for a DRAM product?

Design validation involves running the DRAM design through a series of functional, timing, and performance tests using simulation and hardware verification tools. I work closely with the testing team to

ensure that the design meets all necessary specifications.

Explanation

Design validation is crucial to ensure that the DRAM product will perform reliably under various operating conditions.

22. How do you prioritize features and trade-offs in DRAM design?

Prioritizing features and trade-offs involves understanding the customer’s needs and the application requirements. For example, in mobile devices, power consumption may be prioritized over speed, while in high-performance computing, speed might take precedence.

Explanation

Balancing design trade-offs is a key responsibility of a product engineer, as it ensures that the final product meets the target use case effectively.

23. What experience do you have with memory interface protocols?

I have experience working with various memory interface protocols, including DDR, LPDDR, and GDDR. These protocols define the data rates, latencies, and power requirements for memory products, influencing the overall system performance.

Explanation

Memory interface protocols are critical for product engineers, as they determine how efficiently DRAM communicates with other components in a system.

24. How do you address signal integrity issues in DRAM design?

Addressing signal integrity issues involves careful routing of signals, minimizing crosstalk, and controlling impedance. I also work with the PCB design team to ensure that the layout meets the necessary electrical requirements.

Explanation

Signal integrity is crucial for ensuring that the DRAM operates reliably at high speeds, especially in modern systems with tight timing margins.

25. How do you test for timing violations in DRAM products?

I use timing analysis tools to test for violations by simulating different operating conditions. This includes testing setup and hold times, clock skew, and data path delays to ensure that the DRAM meets timing requirements under all conditions.

Explanation

Testing for timing violations helps prevent performance degradation and ensures the stability of the DRAM in various applications.

26. How do you handle the verification of a DRAM controller?

Verification of a DRAM controller involves creating test benches that simulate the controller’s interaction with the memory and other components in the system. I use formal verification methods to ensure the correctness of the design under all possible conditions.

Explanation

Verifying a DRAM controller is essential to ensure that the memory operates correctly with the rest of the system, avoiding data corruption or failures.

27. What steps do you take to reduce manufacturing costs in DRAM production?

To reduce manufacturing costs, I focus on design-for-manufacturability (DFM) techniques, optimizing the layout for high yields and low defect rates. I also work with the supply chain to source materials and components cost-effectively.

Explanation

Cost reduction is a key objective in semiconductor manufacturing, as it directly impacts the competitiveness and profitability of DRAM products.

Build your resume in 5 minutes

Our resume builder is easy to use and will help you create a resume that is ATS-friendly and will stand out from the crowd.

28. How do you address latency issues in DRAM?

Latency in DRAM can be addressed by optimizing the memory controller, using techniques like prefetching and pipelining to hide latency. Reducing the access time of memory cells and improving the efficiency of refresh cycles are also important strategies.

Explanation

Reducing latency is crucial for improving the performance of DRAM, especially in applications that require fast memory access times.

29. How do you evaluate the performance of DRAM in real-world applications?

I evaluate the performance of DRAM in real-world applications by running benchmarks and stress tests in target systems. This allows me to measure metrics like bandwidth, latency, and power consumption under typical workloads.

Explanation

Real-world performance evaluation ensures that the DRAM product meets the specific needs of the target application, whether it’s for consumer electronics or enterprise systems.

30. How do you ensure compatibility between DRAM and different CPU architectures?

Ensuring compatibility involves understanding the memory access patterns and requirements of different CPU architectures. I work with the system architects to ensure that the DRAM is optimized for the specific CPU, whether it’s ARM, x86, or RISC-V.

Explanation

Compatibility with various CPU architectures is important for ensuring that the DRAM can be used in a wide range of devices and applications.

31. How do you approach optimizing DRAM for performance?

Optimizing DRAM for performance involves tuning parameters like clock speed, data rate, and latency. I also focus on improving the efficiency of the memory controller and reducing the impact of refresh cycles on overall performance.

Explanation

Performance optimization is a key responsibility for a DRAM product engineer, as it directly impacts the speed and efficiency of the memory system.

32. Can you explain the concept of DRAM bank interleaving?

Bank interleaving in DRAM is a technique that improves performance by allowing simultaneous access to multiple memory banks. This reduces the impact of access latency by distributing memory requests across several banks.

Explanation

Bank interleaving is a critical technique for improving memory performance, particularly in high-throughput applications like gaming and data processing.

33. How do you handle power integrity issues in DRAM design?

Power integrity issues are addressed by ensuring that the power delivery network is properly designed, with adequate decoupling capacitors and well-designed voltage regulation. I also work to minimize noise and voltage fluctuations in the system.

Explanation

Maintaining power integrity is essential for ensuring the stability and reliability of DRAM, particularly in high-performance applications.

34. How do you optimize DRAM for mobile devices?

Optimizing DRAM for mobile devices involves reducing power consumption through techniques like deep power down modes, lowering operating voltage, and optimizing refresh cycles. Ensuring low latency is also important for smooth user experiences.

Explanation

Mobile devices have strict power and performance requirements, and optimizing DRAM for these conditions is essential for long battery life and efficient operation.

35. Can you explain the impact of process variation on DRAM performance?

Process variation refers to the small differences in semiconductor manufacturing that can impact the performance of DRAM. These variations can lead to differences in speed, power consumption, and yield, requiring design adjustments to compensate.

Explanation

Understanding process variation is critical for DRAM product engineers, as it impacts the reliability and consistency of the final product.

36. How do you work with cross-functional teams in DRAM development?

I collaborate with cross-functional teams including design, manufacturing, quality, and testing teams to ensure that the DRAM product meets all specifications. Effective communication and problem-solving are key to addressing issues that arise during development.

Explanation

Cross-functional collaboration is crucial in complex projects like DRAM development, where input from multiple teams is required to ensure success.

Conclusion

The role of a Micron DRAM Product Engineer requires a deep understanding of memory technologies, problem-solving skills, and the ability to work effectively with cross-functional teams. By preparing for your interview with these top 36 questions and understanding the nuances of each topic, you’ll be better equipped to demonstrate your expertise and secure your place at Micron. Focus on both technical knowledge and soft skills, and you’ll stand out as a strong candidate for this exciting and challenging role.

Recommended Reading: