Physical design is an essential step in the Very-Large-Scale Integration (VLSI) design process. It involves translating the logical design of circuits into a physical layout that can be implemented on a silicon chip. Physical design engineers need to have a deep understanding of electronic circuits, semiconductor devices, and computer-aided design (CAD) tools to ensure that the circuit functions correctly and efficiently.

During an interview for a physical design position, you may face questions that test your technical expertise and problem-solving skills. In this article, we will cover the top 31 physical design interview questions that will help you prepare effectively.

Top 31 Physical Design Interview Questions

1. What is physical design in VLSI?

Physical design is the process of converting a logical design, described in hardware description languages like Verilog or VHDL, into a physical layout that can be fabricated on a chip. It involves several steps such as partitioning, floorplanning, placement, routing, and verification to ensure that the design meets timing, power, and area requirements.

Explanation: Physical design is a crucial phase in the chip design process where engineers create a blueprint of the design that can be fabricated on silicon.

2. Can you explain the different stages in the physical design process?

The physical design process consists of five key stages: partitioning, floorplanning, placement, routing, and verification. Partitioning divides the chip into manageable blocks, floorplanning arranges them on the chip, placement fixes their positions, routing connects them, and verification ensures the design meets constraints.

Explanation: These stages ensure the efficient organization of circuits on the chip, optimizing performance and manufacturability.

3. What is floorplanning, and why is it important?

Floorplanning is the process of deciding the positions of different functional blocks on a chip. It is important because it affects the chip’s performance, power consumption, and area. A good floorplan minimizes wire lengths and ensures signal integrity while optimizing for timing.

Explanation: Effective floorplanning is critical as it lays the foundation for the subsequent placement and routing steps in the design process.

4. What are the main objectives of placement in physical design?

Placement is the process of fixing the positions of standard cells and other blocks on the chip. The primary objectives of placement are to minimize wire lengths, ensure proper signal timing, reduce power consumption, and avoid congestion in the routing process.

Explanation: Good placement is crucial for optimizing performance and reducing the overall chip area.

5. What is congestion, and how does it affect physical design?

Congestion refers to areas on the chip where too many wires or cells are placed too closely together, leading to routing difficulties. High congestion can result in increased delay, power consumption, and routing complexity, making it harder to meet design constraints.

Explanation: Congestion must be managed carefully to avoid timing violations and signal integrity issues.

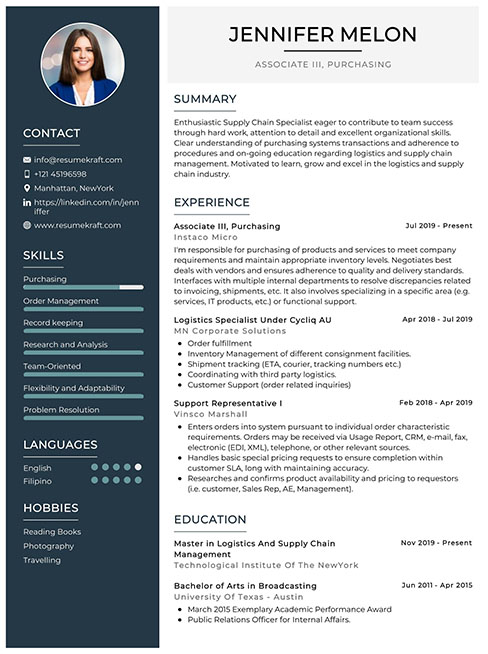

Build your resume in just 5 minutes with AI.

6. Can you explain the concept of timing closure?

Timing closure is the process of ensuring that a design meets all its timing requirements. This involves adjusting the design to reduce delays, fixing violations, and ensuring that data paths are correctly synchronized. Achieving timing closure is critical for the design’s functionality.

Explanation: Timing closure is one of the most challenging tasks in physical design, requiring optimization of logic, placement, and routing.

7. What is clock tree synthesis (CTS)?

Clock Tree Synthesis (CTS) is the process of designing the clock distribution network to ensure that the clock signal reaches all sequential elements (flip-flops) with minimal skew and delay. The goal is to distribute the clock signal efficiently across the chip.

Explanation: CTS is essential to ensure that the clock reaches all parts of the chip without causing timing violations.

8. What is setup time and hold time in VLSI?

Setup time is the minimum time before the clock edge when the input signal must be stable, and hold time is the minimum time after the clock edge when the input signal must remain stable. Violations of these times can cause incorrect data to be latched.

Explanation: Both setup and hold times are critical for ensuring correct data propagation and synchronization in digital circuits.

9. What are design rule checks (DRC)?

Design Rule Checks (DRC) are a set of checks used to ensure that the physical layout of a chip meets the manufacturing requirements. DRCs check for violations such as spacing between wires, minimum width, and alignment issues that could affect manufacturability.

Explanation: DRCs are vital to ensure that the design can be fabricated correctly and without defects.

10. What is the role of parasitic extraction in physical design?

Parasitic extraction is the process of calculating the parasitic capacitances and resistances of the interconnects on the chip. These parasitics can affect signal timing and must be accounted for during timing analysis to ensure the chip meets its performance goals.

Explanation: Accurate parasitic extraction is crucial for ensuring timing accuracy and signal integrity.

11. What is ECO (Engineering Change Order) in physical design?

ECO refers to last-minute design changes that are implemented after the physical design is completed. These changes could be due to timing issues, functional bugs, or power optimizations. ECOs are typically handled by making small adjustments to the existing layout.

Explanation: ECOs are common in the physical design process as last-minute optimizations or fixes are often needed to meet design goals.

12. What is IR drop, and why is it important in physical design?

IR drop refers to the voltage drop that occurs when current flows through the resistive elements of the power grid on the chip. Excessive IR drop can cause the voltage to fall below required levels, leading to functional failures and reduced performance.

Explanation: Managing IR drop is essential to ensure that all parts of the chip receive adequate power to operate correctly.

13. Can you explain signal integrity and how it is ensured in physical design?

Signal integrity refers to the quality of the electrical signals as they travel through the interconnects. Poor signal integrity can result in noise, delay, and data corruption. Ensuring proper routing, shielding, and avoiding crosstalk are some ways to maintain signal integrity.

Explanation: Signal integrity issues must be mitigated to prevent delays, glitches, and functional errors in the chip.

14. What is the purpose of power grid design in physical design?

The power grid is designed to distribute power efficiently across the chip, ensuring that all circuits receive the necessary power. A well-designed power grid minimizes voltage drops and prevents power supply noise from affecting the chip’s performance.

Explanation: Power grid design is critical for maintaining the stability and reliability of the chip’s operation.

15. What is metal layer stack, and why is it important?

The metal layer stack refers to the arrangement of different metal layers used for routing signals on the chip. Each layer has specific characteristics such as thickness, resistance, and capacitance. The choice of metal layer affects routing efficiency and signal integrity.

Explanation: Understanding the metal layer stack helps in designing efficient routing strategies that minimize delay and power consumption.

16. How do you minimize crosstalk in a chip design?

Crosstalk occurs when signals in adjacent wires interfere with each other, causing noise and delay. To minimize crosstalk, designers use techniques such as increasing the spacing between wires, using shielding layers, and controlling signal rise times.

Explanation: Crosstalk mitigation is essential for maintaining signal integrity and preventing timing violations.

17. What is RC delay, and how does it affect signal propagation?

RC delay is the delay caused by the resistance (R) and capacitance (C) of the interconnects in the chip. It affects the speed at which signals propagate, leading to slower data transfer and potential timing violations.

Explanation: RC delay is a key factor in timing analysis and must be minimized to ensure fast signal propagation.

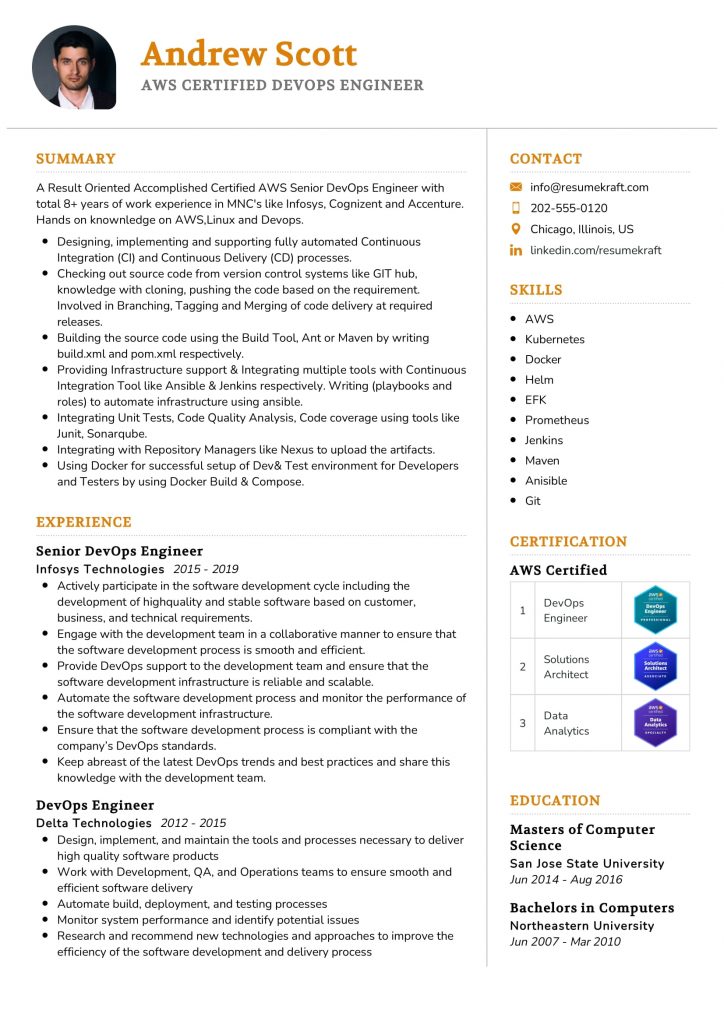

Build your resume in 5 minutes

Our resume builder is easy to use and will help you create a resume that is ATS-friendly and will stand out from the crowd.

18. Can you explain the concept of wireload models?

Wireload models estimate the parasitics (resistance and capacitance) of wires based on the number of fanouts and the size of the circuit. These models are used during early design stages when detailed routing information is not yet available.

Explanation: Wireload models provide a rough estimate of wire parasitics, helping designers make early timing predictions.

19. What is design for manufacturability (DFM)?

Design for Manufacturability (DFM) is a set of guidelines and techniques used to ensure that the physical design can be manufactured reliably and cost-effectively. It includes considerations like avoiding small features, ensuring sufficient spacing, and minimizing process variations.

Explanation: DFM ensures that the chip design can be fabricated with high yield and minimal defects.

20. What are metal fill and its purpose in physical design?

Metal fill refers to the addition of dummy metal shapes in empty areas of the chip to improve the planarity of the wafer during fabrication. These fills help in achieving uniformity in the manufacturing process and prevent defects.

Explanation: Metal fill is a technique used to ensure consistent wafer thickness and improve yield during fabrication.

21. What is latch-up in CMOS circuits?

Latch-up is a condition in CMOS circuits where a parasitic structure forms a low-resistance path between power and ground, leading to high current flow and potentially damaging the chip. It is prevented by using guard rings and proper layout techniques.

Explanation: _Latch-up can cause severe damage to a chip, so it must be avoided through careful layout

design._

22. What are corner cases in timing analysis?

Corner cases refer to extreme conditions in timing analysis that test the design’s performance under different operating conditions such as variations in voltage, temperature, and process. These cases help ensure that the chip functions correctly under all conditions.

Explanation: Corner case analysis is critical to ensure the robustness of the chip under real-world operating conditions.

23. Can you explain the difference between static and dynamic IR drop?

Static IR drop refers to the voltage drop that occurs under steady-state conditions, while dynamic IR drop occurs due to switching activity in the circuits. Both must be minimized to ensure stable power supply and prevent functional failures.

Explanation: Both static and dynamic IR drops can affect the performance and reliability of the chip.

24. What is electromigration, and how does it impact chip reliability?

Electromigration is the gradual movement of metal atoms in a conductor due to high current density, leading to the formation of voids and eventual failure of the wire. It is a significant reliability concern in chip design and must be managed carefully.

Explanation: Electromigration can cause long-term reliability issues and must be accounted for in power grid and routing design.

25. How does power gating help in reducing power consumption?

Power gating is a technique used to reduce power consumption by selectively turning off the power to certain parts of the chip when they are not in use. It is particularly useful in low-power designs where power efficiency is critical.

Explanation: Power gating is an effective way to reduce leakage power and improve the overall energy efficiency of a chip.

26. What is the role of buffers in physical design?

Buffers are used in physical design to drive long interconnects, restore signal strength, and meet timing requirements. They help in reducing delay and maintaining signal integrity over long distances on the chip.

Explanation: Buffers are essential for optimizing signal propagation and ensuring that timing constraints are met.

27. What is a scan chain, and why is it used?

A scan chain is a series of flip-flops connected in a chain to facilitate testing of the chip. It is used in Design for Testability (DFT) to check the functionality of the design and detect any faults after fabrication.

Explanation: Scan chains are a key feature of DFT that enable efficient testing and fault detection in chips.

28. How is power analysis performed in physical design?

Power analysis in physical design involves estimating the power consumption of the chip based on its switching activity, leakage, and parasitic capacitances. It helps in identifying power-hungry areas and optimizing the design for better power efficiency.

Explanation: Accurate power analysis is critical for ensuring that the chip meets its power budget and thermal requirements.

29. What are metal layer vias, and how do they affect performance?

Metal layer vias are vertical connections between different metal layers used in the routing process. The quality and number of vias can affect signal delay, resistance, and reliability, making it important to optimize their placement.

Explanation: Vias play a critical role in connecting metal layers and ensuring efficient signal routing and power distribution.

30. What is thermal management in physical design?

Thermal management refers to techniques used to control the heat generated by the chip during operation. This includes optimizing the power grid, using heat sinks, and designing for even heat distribution to prevent thermal hotspots.

Explanation: Thermal management is crucial to prevent overheating and ensure the chip operates reliably under different conditions.

31. What is chip packaging, and why is it important?

Chip packaging involves enclosing the silicon die in a protective case that provides electrical connections to the outside world. It protects the chip from environmental factors and mechanical stress, ensuring reliable operation over its lifespan.

Explanation: Packaging is the final step in the chip design process that ensures the chip is ready for integration into electronic devices.

Conclusion

The physical design interview process tests a candidate’s understanding of VLSI concepts, CAD tools, and optimization techniques. Being well-prepared for these interviews requires a strong grasp of key topics like timing closure, signal integrity, and power management. We hope that these 31 interview questions and answers have provided you with a solid foundation to ace your upcoming interview.

For more career resources, explore our resume builder, free resume templates, and resume examples to elevate your professional journey. Best of luck with your interview!

Recommended Reading: